# **Computer System Architecture**

#### FOR DIPLOMA STUDENTS

Notes Prepared by RABI KUMAR DARJI IT Dept.

JHARSUGUDA ENGINEERING SCHOOL, JHARSUGUDA

## BASIC STRUCTURE OF COMPUTER HARDWARE

02-21-10.2021

A computer system is besically a machine that simplifies complicated Jarks. It should maximize performance and reduce costs as well as power concomption. The different components in the computer System Arti Architecture are input unit, Output unit, Storage unit, Asithmetic Logic Unit, control entitete.

INPUT INPUT UNIT INPUT INPUT UNIT INPUT

The input data travels from input to ALV. Sinilarly, the computed data travels from ALU to output wit. The data constantly moves from storage unit to ALU and back again. This is because stored data is computed on before being stored again. The control unit controls all the other unit as well as their data. MUMPER ANTUMNO TO MUTOUTTE DILLE

INPUT UNIT a verset and a real plication of any person and The input unit provides date to the computer system from the outside. So, basically it links the external envitoment with the computer. It takes date from the input devices, converts it into machines longuage and then loads it into computer system. Keyboard mouse etc., are the most commonly used input devices. Arr Ita South in U

#### OUTPUT UNIT

The output unit provides the results of computer process to the users in it links the computer with the computer environment. Most of the output data is the form of audio or victo. The different output durices are monitors, printers, speakers, headphong etc.

1111

#### STORAGE UNIT

1 POIL Storage unit contains many computer components that are used to store data. It is traditionally divided into primary storage and secondary storage. Primary storage is also known as main memory and is the memory directly accessible by the CPU. Secondary storage or external storage is not directly accessible by the CPU. The data from secondary storage before the CPU can use it. Secondary storage contains à large amount of data permanently. ARITHMETIC LOGIC UNIT . The many - Ware

All the calculations related to the computer systems are performed by the out thmetic logic unit. It can perform operations like additions, substraction, multiplication, division etc. The contrud

unit transfers dater from storage unit to arithmetic logic unit when calculations needs to be performed. The arithmetic logic unit and the control unit together form the central processing unit.

### CONTROL UNIT

The unit contracts all the other unit of the computer system and so is known as its central nervous system. It transfers data throughout the computer as required including from stonge unit to central processing unit and vice verse. The control unit also deded diceter now the memory, input, ou put cluvices, withmetic logic unit etc. should behave. (sequency execution of instruction is done by control unit). Size of Memory

1 byte = 8 bit 1Kb = 1024 byte 1mb = 1024 Kb 1mb = 1024 × 1024 byte 1gb = 1024 × 1024 <del>byte</del> 1Gb = 1024 × 1024 <del>byte</del> Kb

1Gb = 1024 × 1024 × 1024 byte

1966 = 1024 × 1024 × 1024 × 8 bit

\* There are more than one register present in

Regfster= 1+ fs smallest memory located in cru

It is smallest capacity memory stored intermedical results.

To find CPI 2 Total CPD Clock cycle for the Program Instruction count τ [<sup>1</sup> Σ<sup>n</sup> 1 + 1 CPIIX II Ic MFLOP = no. of floating point operation in a program Execution time X100 10°= million (mega is known as 10°) Instruction count MIPS = 1.1.1.1推 (Finite Fill) "推动 Execution time X106 -) IF a computer A twins a program in Osec & computer B twins the Same program in Ssee them. How much Faster is B than A. Sol, Penformance = Execution time Contractor and a second ar purformance & execution time Participate a start start a free 1 free 1 get A= 10ses B= 5sec Execution time OF A [EA> EB] then Performance OF A PAX PB  $= \frac{P_A}{P_B} = \frac{\frac{1}{10}}{\frac{1}{15}}$ 10 x 5 all white book  $\frac{P_A}{P_B} = -$ PB = 2BA m

Dt: 11.11.21

RAM (Random Access Memory) RAM is a hardware element where the date being currently used is stored. It is a volatile memory. The data on the transform access memory can be read, written and enased any times number of times. ypes of RAM :-MAN (1) Static RAM: - Stores a bit of data using the state OF a six transistor memory cell. (SRAM) (i) Dynamic RAM: - Stores a bit data using a pair of transistor and capacitor which constitute à DRAM memory ul ROM (Read Only Memory) ROM is a type of memory where the data has been pretecorded. Data stored in ROM is retained even after the computer is turned off or also known as non-volatile memory Types OF ROM () PROM - ( Programmable Read only memory) (i) EPIROM -> (Erasable Programmable Read only rumory) (iii) TEEPROM -> ( Electrically erasebble programmable KOM) () UVEPROM -> (ultra-violet EPROM) Difference between RAM and ROM RAM ROM RAM is a volatile memory >ROM is a non-volatile memory -> It could store the data as long , it could retein the data even when > as power is supplied power is turned off -> RAM can be retrived and altered -> Data stored in ROM can only be read -> It is much slover than RAM -> It is a high speed memory a small insize with less capacity and - Largen in size with higher cheaper than RAM capacity and costlies

| ,                                                                                                                | SRAM (Static RAIM)                                        | DRAM (Dynamic RAM)                                                                                   |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| ÿ                                                                                                                | Stories information as long as<br>power is supplied       | Stores information only for few<br>mili-seconds even when power is<br>supplied.                      |

| ii>                                                                                                              | It is made up off flip-flop and<br>many transistores      | It is made up off carpacitor and<br>Few transistors.                                                 |

|                                                                                                                  |                                                           | Bit stored in the form of eluchic charge                                                             |

| iv>                                                                                                              | It has no leakage property so<br>does not need to refresh | it needs to be refreshed                                                                             |

| v)                                                                                                               | Refreshing circuit is not implemented                     | Refreshing circuit is implemented                                                                    |

|                                                                                                                  | For a single memory cell, six<br>transistor are used      | For a single memory cell, one transist<br>or is used                                                 |

| vii>                                                                                                             | faster than DIRAIM                                        | Slower than SRAM                                                                                     |

| viiv                                                                                                             | More expensive than DRAM                                  | Cheaper-than SRAM                                                                                    |

| 1                                                                                                                | Size of memory cell is larger                             | cheap size of memory cell & smaller                                                                  |

| ×〉                                                                                                               | It has low density (memory                                | 11 has high density                                                                                  |

| ()                                                                                                               | cell per avea)<br>17 is used is cache memory              | 14 is used in main or primary<br>memory that is DIDR, DDR2,<br>DDR3 (DDR= double clata rate)<br>room |

|                                                                                                                  | ÷                                                         |                                                                                                      |

| n degeneration of the second |                                                           |                                                                                                      |

|                                                                                                                  |                                                           |                                                                                                      |

|                                                                                                                  |                                                           |                                                                                                      |

CAMPER AND 12 MEMORY ADDRESSUNG Two types () Word addressing: Combination of several bit meserenal by the are known as word adduessing ii) Byte addressing: World addressing Ex -> 4096 x 32 1, NO. of bytu/block Ésize of block WORD addressing Each cell conteins one word Byte addressing First block represent word location ++ i j+1 j+2 J+2 j+4  $l = \int_{-\infty}^{\infty} dr r dr r dr$ 1+1= j+4 j+2=j+8 4096832 (4 byte, so, 4 block) word= 32 bit 4096 = 212 / 12 bit needs to store) word addressing () 4096×32 (iii) 1024 x 32 = 2" × 22 212 ×4byte 212 × 22 = 212 2'4 (1) 256 ×16 (i) 4096 x 16 = 2 × 2 = 212 v2 byte 29 B 212 x 2 byte = 2'3

DE= 17.11.21 TENIDIAN Two types () Little Endlan (INTEL PROCESSOR) DD BB. cc AA lower \_\_\_\_\_, higher ( M. Big Enclian (MAC, AMD) BB AA DI) ce 1 111 0 lower \_\_\_\_\_\_ higher inter in Shine Tre Ex > start int = OXAABBCCOD and see how you will be a the leart significant Byte (LSD) = DD Maximum significat Byte (MSB) = AA CHAPTER = 2 INSTRUCTIONS Instruction :- Commands given by computer april and + Manna He provide Three types and with a work of the () MODE -> It specify whether the address is direct or (i) OPCODE -> Operation performed by ALU for ex or mathematics indirect operation l'expression performed known as OPCODE for ex-t, -, +, x. @ OPERAND > contains direct and indirect address. -> direct address / indirect address \_NO Fire location Pointer: A variable which hold the address of another variable Instruction contains - () Memory ruggerence Pristruction MODE OPLODE OPERAND

#### COMPUTER INSTRUCTIONS

Computer metruchions are a set of mochine language instruction that a particular processon understands and executes. A computer performs tasks on the basis of the instruction provided. An instruction compresses of groups called fields. These field include: • The operation code (OPCODE) Field which specifies the operation to be performed · The address file which contains the location of the operand, that is neglister or memory location. · The mode field which specifies how the open and will be located. -> A basic computer has three metruction code formats which ou:-(1) Memory instruction - I OPCODE ADDRESS (i) Register Instruction - 0111 Register Oper" (i) Input - Oelpert instruction ("Junimit or up) 1000 -> Memory - reference instruction: - In this instructions are represented by the open 12 bits of memory is used to specify an address and one bit to specify the addressing mode "I'. → Registur - regenence fortwichon OPCODE Register 2 byte = 16 bit Addressing operation mode  $3 \text{ bit} - 0 \text{ puble} = 2^3 = 3$  $(\mathbf{I})$ 12 11 I:0, oprode= 111, code= 7400 000 = ANDCAL = Clear Accumulator (Register) 001 - ADD 010 = LOND CLE - clear R (Regrister) CNA= complement Accumulator E 011 = STA 101 = BUD (Branch) and Accumulator is a register. 11 0 = 152 111

-> INPUT- OUTPUT INSTRUCTION :-小口 计图题 Reggi ter - reference instruction :-1144 0111 Register opera" Verto The register- requerer instruction are represented by the opcode 111 with a O in the leftmort bit (bit is) of the ins-truction. A register - reference instruction specifies an operation on a test of the AC (Accumulator) register and the INPUT OUTPUT INSTRUCTION :-An Input-output instruction does not need a reference to memory and is recognised by the operation code 111 with a 1 in the leftmost bit of the instruction. The runaining 12 bits are used to specify the type of input-output operation performed. INP- F800 - Input Addressing OPCODE Input/output character to AC (Accumulator) operation 111 mode (I) 12 11 14 15 T=1 ,111 FLANER OF KILLISTER · Types of Instruction :astronomy we have a (i) Data Transfer Instruction (1) Data Manipulation Instruction in the top top prophet is Dergram control Instruction Data Transfey Instruction: - This instruction is used to transfer (() data from one location to another location without changing binary information content NAME MNEMONIC the LD LOAD 5 1 STORE MOV MOVE IN MPUT PUSH PUSH pop POP

(i) Data manipulation Instruction: - These instruction performed ouithmetic, logic and shift opuration. NAME , MNEMONIC Clean UR AND AND OK OR-X-OR St. and compliment WM EX-OK X-OR (ii) Program control instruction: - These instruction provide decision making capability and change the path taken by the program, when executed by computer NAME 1 MINEMONIC JUMP JMP SKIP SKP 1111 RETURN RET TYPES OF REGISTER DE-23.11.21 -> Memory Address Register -> Tar I have -> Memory data rugister - Accumulator -> Program counter > Memony Butter Register (MBR) > this instruction register

Phogham Counter Register: - Program counter/reegister holds the address of next instruction to be Computer Register : Register holds an important position in computer autitecture. These are temporary storage area in the computer, where the newly fetch doit is stored. A register is sequential circuit. Registurs are group of Flip-Flops where each flip-flop stones one bit of information lypes Program counter register :- 11 holds the address of the next instruction to be fetched. ·Instruction is fetched from the address specified by the program once the instruction is fetched then the value with each operation program counter increments its value Memory Adre Address Register:-It is a combinational circuit that holds the as memory address It tells the computer which by the of information to find in 17 1's also stone the address where the data will be Instruction Register: - It is a part of a CPU. that holds an in memory Mstruction before executed. Once the instrance is fetch from the memory the Retached instr is store in instrin negister. Decoder is connected with this init negrister is decode the fetched inst<sup>n</sup>.

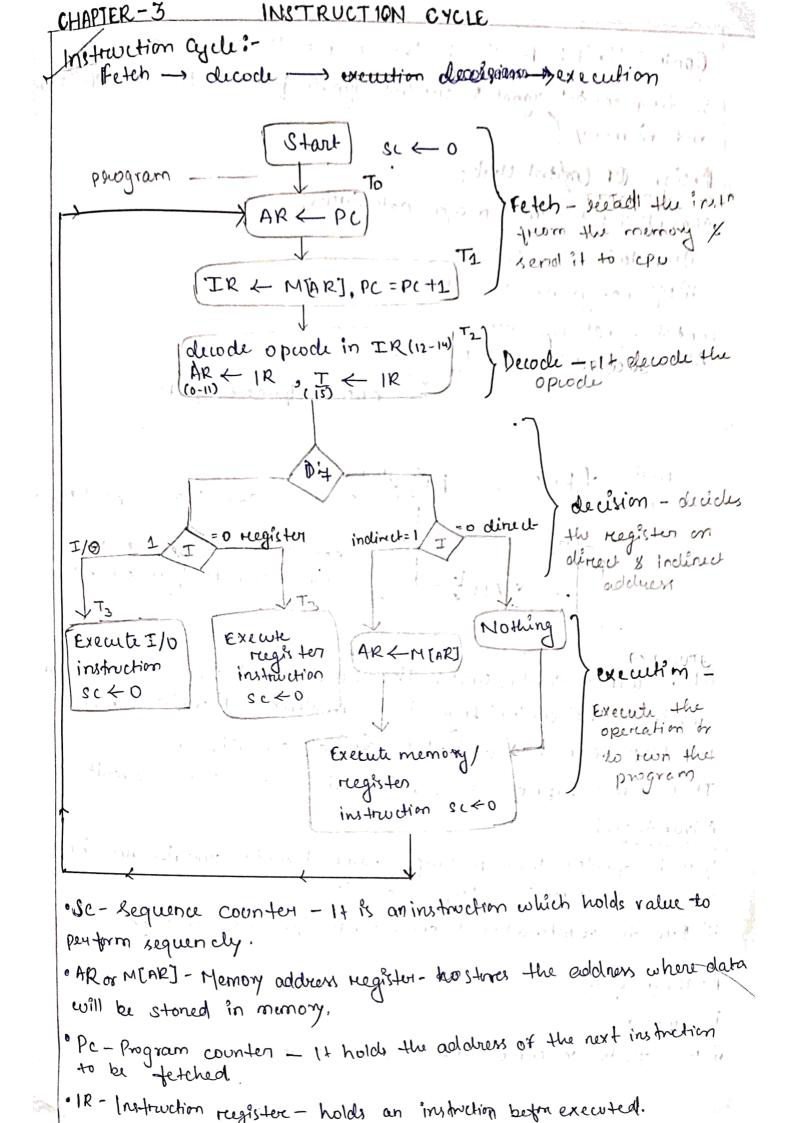

Memory Buffey Register = This register is used for beoffering of the memory so that instruction is not halted abruptly to the processor. Memory Deta Register = When an instruction is decoded, then we get the information about speade, made and address field > This address field provides the informal- either directly or indirectly about the address of the operand. - when the openand address is found out the operand is fetched from that address and this operands is stoned in a register known as memory data neglister Accumulaton: - It is a type of register that are stoned by CPU. Accumulatori acts as a temporary storage location which notals an intermediate value in mathematical & logical calculation Keywords :-M. D. Oa Tetch - An instruction of is fetched from the memory 201.0001 picking an instrant to the from the menory Decode - The instro is fetched from the memory after theit instruction is decoded so that instruction can be interpreted. in this phase, CPU finds out the operation to be performed and this operation is denoted by an opende. Texecute: - Once the operation is identified during the decoding phase then the arithmetic × logical curit performs that operation & the result is stoned in memory from where the nesult-is displayed to user.

Dt=25.11.21

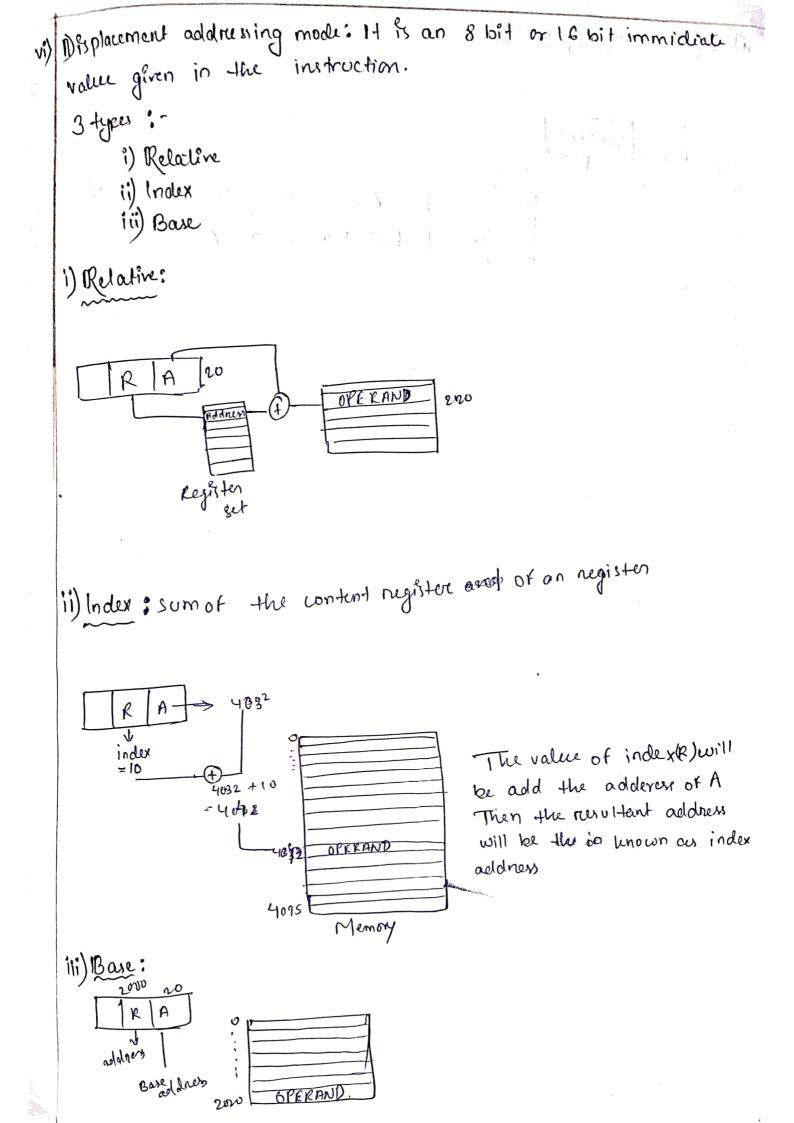

Addrussing Mode: - [8086] The term addressing mode refers to the way in which the operand of an instruction is specified. The addressing mode specifies a rule for interpreting or moditying the address field of the instruction before the openand is actually executed. Types Of Addressing Mode:white the one the ) Immidiate addressing mode ii) pirect addressing mode iii) Indirect addressing mode. 9v) Register addressing mode v) Displacement addressing mode (relative, index, based addressing) vi) Stack addrening mode. i) Immidiate addressing mode :- in this mode date is present in address field of instruction. Designed like one address instr format. OPERADO -> Direct data in this addressing mode data is directly stored here. ii) Dérect addressing mode Absolute addressing Mode ():- in this addressing mode the 16 bit affective address of data is the of the intraction. part addressing node only one memory requience operation in this is required to access the data Monory Instran

\* Reffective address refers to the location of operand

Data

Effective address

ii) Indirect addressing mode (@,1): - In this mode address field of instruction contains the address fields of affective address. Hore two reefarmers are requêred. DRegister Andirect: In this effective address is in the register, and corresponding register name will be mainteined in the address field of an instruction. The test \* Here only one memory reference is required to access the date i) Memory Indirect: In this effective address is in the memo memory, and coursesponding negister name will be main-tenned in the address field of an instruction. \* yere as two memory reference is required to access the data iv) Register addressing mode :- In this addressing the operand is placed in one of 8 bit or 16 bit general purpose registers. The date is in the negister that is specified by the instruction \* Here one register reference is required to access the data R personal pregistor cells unique register/ specific register v) Register indérect mode: In this addressing the operand's offset is placed in any one of the registers (BX, BP, SI, DI) as specified in the instruction. The effective address of the data is & in the base register or an index register that is specified by the in struction \* Here two registor reference is required to access the data 0 PERAND R

of holds the address of another address or operand.

Stack addressing mode: vi) Always holds the address of first two memory. OPERAND 32

INC MALE MALL

at a company of the construction of the construction of the

ing MSA

Dt + 14 - 12 - 21 ii) Micropriogrammed contrible unit .-Ni uno-instructions It con-terms nuro-operations i) It is implemented using programming approach. ii) A sequence of micro-operations are cauried out by executing a program consisting of micro-instructions. iii) Miuro-programmed are stored in a memory of control unit as control memory. iv) Execution of micro-instruction is responsible for generation of control signal. PERSONAL PROPERTY ADDRESS \* Antitechture of nicuoprogrammed control cent:conteins all addness Next address External. control ontrol control contruo 1 generatore input aldress word defe nemory Sequencer negisto ROM Fetch + code whitten in binary to perform instructions, each instructions has their own & different code, there code are not constant, it changes according to code size & numbry. \* The address of nurve - instruction is that is to be executed, it stoned in contruol address negisture This nucleo-instruction contains control word to executed one or more nievo-operations. \* Aiftor the execution of all micro-operation of micro-instruction the address of next nuicro-instruction is located.

## \* Advantages of niverpringrammed instruction: \* It is less complex in desing because niverprogram is implement, using software resultine. \* It is none flexible because desing, modification, construction & enhancement is easily possible. \* less enviore to implemented \* Disadvantages \* It is closen than hardwined control unit, because it takes more time to generate control signals

Memory System Chapter 1 Memory heericanchy and chance leristics :-In the computer system design, memory hierarchy is an enhancement to orgunize the memory such as that it can minimize the laccess time. The memory hierarchy was devloped based on a Pragram behavion known as locality of neferences. The figure below cheanly demonstrates the different level of memory hierarby A MARTINE A FIRST and a sub- miles 1 ja j 34. 🕐 Sta Marine + H Thenease, in Register alless time, cost increase in \$ capacity per bit cause Primary 15 11 1961 3 memory-A CHARGE STATE STATE STATE 1.16 1. 1111 Secondary memory Extended memory on secondary memory ? " comparising of magnetic deser Disk , may nefic Tapie Tapel : e perdiphenal stonage devices which are accessible by the proceedor. vice Ja module. Thennal memory on primary memory Compressing of main memory, cache memory and CPD register. I This is directly accessible by the processor. We can inter the following characteristics of memory hieranchy design from above figure. Cathle Memory It is the memory which is very nearest to CPU; all the recent instruction are stored into cache momony. Processor cache moin memory. Registen :-21 37 3 46 16 12 A server a star

Address Bus a component 3 4 6 5 B 10 9 メベブ X XX X 0 O 0 RAML i spece \* \* \* \* \* \* × 0 1 O RAM 2 ÷. O X X X X X X O 1 X X X X X X X X 1 0 RAM 3 \*\*\*\* RAMY ١ 0 XXX ROM X 12 1 3 1 1 1 1 1 1 1 1 1 1 . 1 + 11 M 1 all and the 1.20 a con the Last an source at Memory connecting to CPU:-Address Bus April 1 14 11 100 11 Dal RD WR 1-1 10 16-11 CSL 125 \*8 Decadea 1:11 14 5.2 52 RAMI RD Dala ADT rest 125\*5 652 RAM2 RD a gaba WR Data AD 11 111 11 CSL 125\*8 1 -11 1.11 CS2 RAM3 RD A10) 71 1 Data Test 128\*8 CS2 RAMY RD IND + Ada . Day pr. n 12/12/ 13511 A THE THE Q1 19615 A Lah are CS1 12578 CS2 ROM 2 - 2 - 2 - 2 - 2 . . . . . In Merrill PDA Data the states a state of the

19 1.1

CACHES MEMORY retro raches memory is placed between main memory and cpu. - 4 + 9 + F L \_ " Carbos memory is small in size and faster memory. of It is contain most frequently access instruction and data "It is located inside the CPU chips on mather bound. CPU Chip L 3 LI cache La cache (External rache) e en ser de la compañía de la (Internal cache) CPU (> LI (-> L2 (> L3 (> RAN) CPUK > Cache (RAM] L'and prover for a state Worthing of cache The CPUT misially lookes for the cathe for other da it the doctor is there ist will netrive, and proce Advis and The data is not there then CPU access the system main memory and puts a copy of a new doited in the entry cache memory put a copy of a new derta in the cache befored processing let. Next time if the CPU needs to access Some date age it will just netrive it thom the cache in speed of going through the hold loading process again CPUK > Leache > RAMA

RAM to cache -> data -> block from cache to RAM -> data -> word from.

Inter Leaver Memority (i) Wide memory organization with singlas memoly module : A singue memory module couse LCPU St sequencial accord to instruction that is only one memory across cache can be perform at a time. memory Primary hance throughtput & may drop. Throughtput is low. Total amount of work done in a given time that is called throughtput. i Paralle + In parouled, Throughtput is high. CPU -\* Memory inter leaved is technique to inchease Cache the throughtput modules P.M IP.M 1PM IP.M ulich ane nead on write mattion is panallaly It is used in DRAM to increase the speed. CPU. Read openation Address Bug memory Address register MAR IMAR IMAR memory module (9) MMJ MM3 IMM2 memory data negister MBRI MDR IMORI data Bus. Advantage is system petitorimaince is enhance become read and writte openation Or curves Simanteinsaly, across module. in a similar 'fashion ! multiple Memory address register nectived information from a Common address Buc. memory douter register. communication with a bia dia tinal U data bus and Addressele bus ( Uniclinetional)

| Functional Table                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------|

| CSI CS2 RD WR memory function state of Data Buy                                                                                    |

| 0 0 x x Inhibit High implement                                                                                                     |

|                                                                                                                                    |

|                                                                                                                                    |

|                                                                                                                                    |

| 1 Read input data & ring                                                                                                           |

| , a l x wrate output ocour to v                                                                                                    |

| 1 1 X X Inhibit High implement.                                                                                                    |

| We can conclude that the unit is in operation                                                                                      |

| only when CS1 = 1 and CS2 = 0                                                                                                      |

|                                                                                                                                    |

| Data Bus state > 0, 1, High impliement.                                                                                            |

| KOM CHIPS                                                                                                                          |

| ROM chips are also available in a variety of size and                                                                              |

| The clip inter consolition is to pool                                                                                              |

| The chip inter connection in siz * 8 ROM.                                                                                          |

| Chipseleitt CSL                                                                                                                    |

| chip select 2 - CS2 512*8 > 8 bit data Bus Roy                                                                                     |

| 9481 addites ADS                                                                                                                   |

| A ROM chip has a similar organization as a RAM chip.                                                                               |

| A ROM can only perform read operation; The data Bu                                                                                 |

| can only openate in an output mode.                                                                                                |

| The g bit address lines in the ROM Chip specify any<br>one of the 512 gite stoned in it.<br>The make for chip select 1 and all all |

| one of the 512 gite stored in it                                                                                                   |

| must be I and QO.                                                                                                                  |

| must be I and QO.<br>The date hus is sail do in and chip septert 2                                                                 |

| The data bus is said to be in a high implicent imped<br>state.                                                                     |

| Gtere.                                                                                                                             |

|                                                                                                                                    |

1. RAM (Random access memory) integrated cineit 2. RON (Read only memory) integrated circuit chips. RUW CHILDS OBGIU. RAM chips are available in a variety of size and and used as per the system requirement. The chip interconnecting in 128\*8 RAM chips. chip select 1\_\_\_\_ CSL chipseleil 2 cst 125\* 8 s bit data bus RAM 1100 × 101 Read RD a de plan Write WR - A.D.T 7-bit address (1) 128 \* 8 RAM clip have a memory cupacity of 128 words. of 8 bit (one byte) per world. Combination of sevenal bit is known as wonds. This nequined a 7 bit of address : (Address slow + AB) and 8 bit of Data Bus (bidinectional) (Data Flow -> DB) is) The 8 bit of Data Bus allow the thansfor of data. In either from memory to CPU during read operation on CPU to memory during a write operation. in the nead and write inputs specify the memory operation, and the two child select includes in the memory operation, and the two chep select (cs) control inputs are For enabling the chip only when the microprocessor ive the bidinectional data Bus is constructed using three. state buffers. (v) The output generalited by three state buffer can be, placed in one of the three possible state which Enclude a signal equivalent to have 1, a signal on a high empendance state equal to 100,

Vapacity : It is the global volume of information the memory can stone. I As we more from to to bottom in the hiercarreny, the access time Increases. Access Time 2 It is the time interal between the read/write nequest and the availability of the data. As we have move from top to bottom, the access time increases. Performance When the computer system was design, without memory Hienanchy design, the speed gap increases between the CPU bregester and main memory due to lourge différence l'an access time. This mesult in lower performance to the system and Thus, the entrancement was made in the form of nequined. This enchancement was made in the From of Memory heranchy Design become of which the performance of the Usystem increase. One of the most significant ways to increase system periformance is minimizing how for down the memory hierandy one has to go to manipulate data. Cost per bit As we move from bottom to top in the dierentery, the cost per bit increase it. Interal memory is costlien than External memory. \* Main Momory is The main memory is acts as a central stonage Unit in a computer system. , if It is lange and fast memory used to stone program and data during the run time operation. The primary mor technology used for the main memory is based on demiconductor integrated cincuit. in The integrated circuit for the main memory ane classified into two major unit.

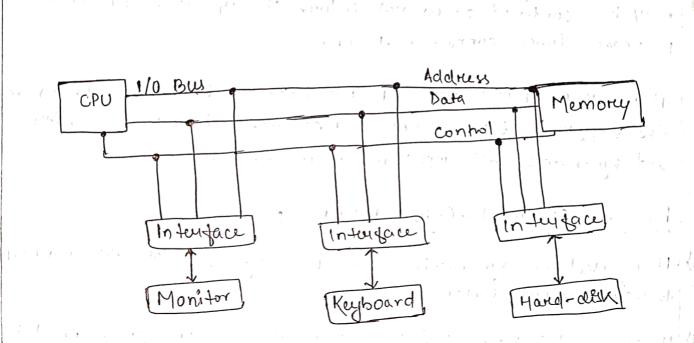

## CHAPTER-4 INPUT OUTPUT INTERFACE

Input Output Interface:

It is used as an method which helps in transferring of information between the internal storage duvices that is memory and the external peripheral duvice. A peripheral duvice is that which provide input and output for the computer. It is also called input output duvices. for ex: A Keyboard, Mouse provide input to the computer are called input duvices, while a monitor and printer that provide Output to the computer are called output devices. Just like the external hand-drives, there is also availablity of some peripheral devices which are able to provide both.

In micro-computer base system, the only purpose of perupheral devices is just to provide special communication linus for the the interfacing them with the CPU. To resolve the differences between peripheral devices and CPU, there is a special need for communication linus.

The major differences are as follows.

1. The nature of peripheral duricy is electromagnetic and electroelectro-mechanical. The nature of the CPU is electronic.

There is a lot of difference in the made of operation of both peripheral devices and CPU, there is a special need for commun links.

|      | キション・ション・ティー・コン・アルフトリー 日本語のないで                                                                                                                                                                                           |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | The major difference are as follows:                                                                                                                                                                                     |

|      | 1. They The nature of percipheral devices is electromagnetic<br>and electro-mechanical. The nature of the CPU is electronic<br>There is a lot of difference in the mode of operation of<br>both peripheral device & CPU. |

|      | 2. There is also a synchronization mechanism because the data<br>transfer nate of peripheral devices are slow than CPU.                                                                                                  |

| ÷.,  | 3. In perupheral devices, data code and formats ance auffor grand                                                                                                                                                        |

|      | the format in the CPU & memory<br>4. The operating mode of perceptural devices are different & each<br>may be controlled so as not disturb the operations of other<br>percipheral devices connected to CPU.              |

|      | There is a special need of the addition havelboare to nesolve<br>the diggerences between CPU and peripheral devices to survives<br>and synchronize all input and output devices.                                         |

|      | Functions OF Input - Output Interface:                                                                                                                                                                                   |

| 1)   | It is used to synchronize the operating speed of CPU with ruspect-<br>to input - output duricus.                                                                                                                         |

| 2>   | It selects the input - output divices which is appropriate for the interpretection of the input - output divices                                                                                                         |

|      | It is capable of providing signals like control & timing signals.                                                                                                                                                        |

| 4)   | In this date buildering can be possible through date bus.                                                                                                                                                                |

| s>   | There are various error detectors.                                                                                                                                                                                       |

| - 67 | It converts digital data into analog signal & vice-versa                                                                                                                                                                 |

|      |                                                                                                                                                                                                                          |

|      |                                                                                                                                                                                                                          |

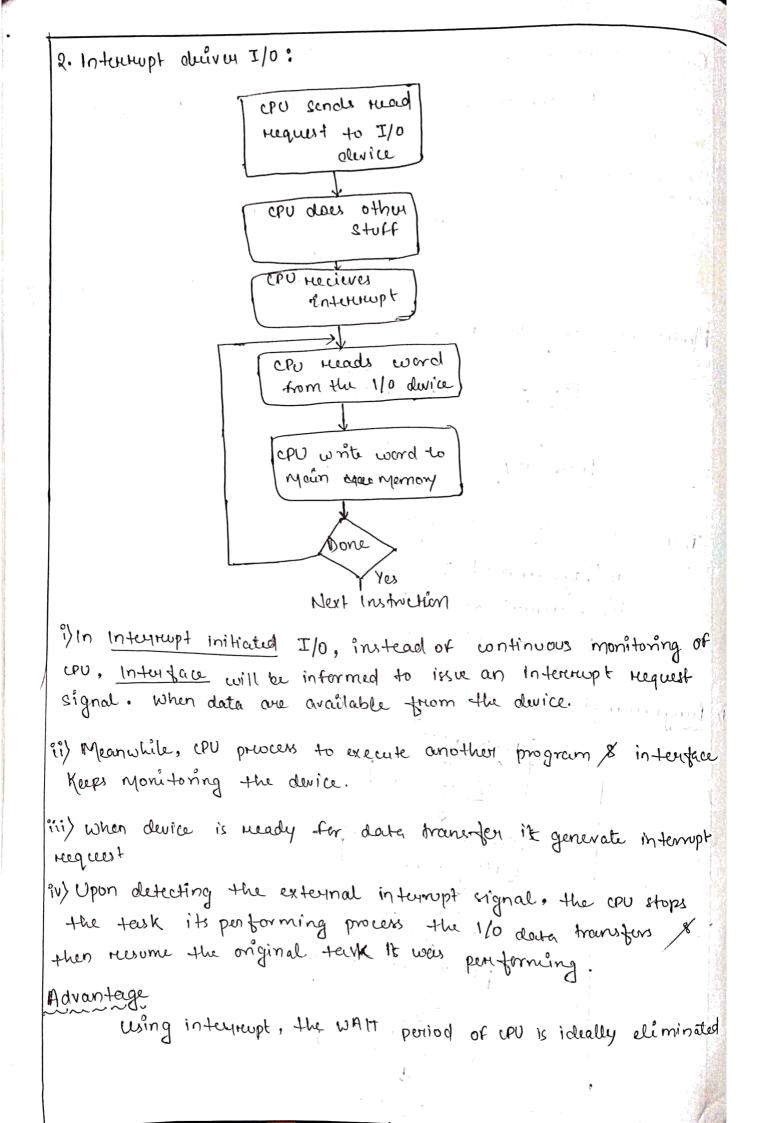

Control command . It shows activate the peripherals & to inform what to do. Status command :-It gives the status of peripherals devices Keyboards, nouse, printer, external Modes of data transfer . T/O devices ICPU K r lemo ky There are 3 types of mode i) Programmed I/0 ii) Interurupt driver I/0 iii) Direct memory access Pubgrammed I/O:î> Issue read command to Jan . in and Gi I/O module 01. All Contract 113 Read the status of I/O Module check status Read word from I/O module Write word into memory Done

3. Direct Memory Access (DMA). CPU MM DMA 1/0 i) In-modeum computers. IDMA is used to transfers large i) The data transfer between a fast storage media such as magnetic disk and memory unit is limited by the speed of the cru. Thus we can allow the perupherals directly communicate with each other using the memory buses, removing the intervention of the CPU. This type of date transfer technique is known as DMA contein Main memory system bus data bus, address bus, CPU control bus DMA controller DMA controller Network dish2 adapter der 1 Actual diagram of DMA Controller IDMA Request BR (Bus request) I/0 DMA CRU controller BG (Bus Grant) MMK i) The direct numbery access (DMA) is a I/O Technique that provide direct access to the main memory while cpu is temporarily desable to speed up the memory operation. ii) The process is managed by chip known as DMA controller (DMAC) iii) I/O devices are connected to system has via a special interitace circuit called " DMA controller".

in DMA both CPU × DNA controller have access to main memory via a shared repter but having data, address & control lines. V) During DNIA therefor the CPU is idle and has no control of the system but or also called memory alass. Bus vi) IDMA therefor is also used to do high speed memory - to -Memory - Manader 1.11.14 How to make cpu in ideal state? (Bus request) BR > BR DBUSK ABUS IDMA . CPU RD >BG WR BG One common Method with 2 specials contrul signeds i) Bus nequest (BR) signal ii) Bus Greant (BG) signal. DMA WONLing: UI/O wants to transfer date with your memory i) DMAC sends IDMA request to IDMA controlley (DMAC) iii) IDMAC would until CPU sends IBGI (Bus Grant) signed to Drug v) CPU refinguishes control of kuses and places address bus (ABus) data Buy (DBW), RD & WR lives into a high impedence state vi) DIMAC takes control of the buses to conduct direct memory -Hansfer without CPU intervention.

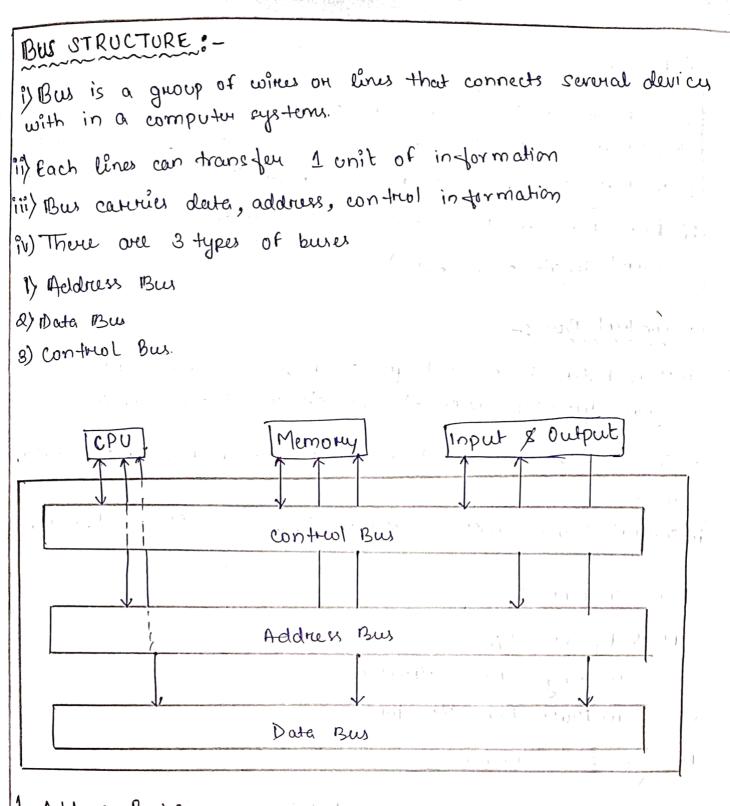

1. Address Bus: i) It is uniclinectional and group of withes which carries address information bits from processon to perlipheral

ii) The address bus with width determines the maximum memory capacity.

ex-11 the address line: 3 bit the 23:8 that is 3 address line required to select & location.

ADD TO THE THE 2. Dale Bus :i) It is bidinedimal and group of wines which contains data information bits from processon to peripherals & vice-versa ii) In this bus data instruction more between CPU & peripherals ii) Data Bus width determine the system putformance (would length of computer) 3. Control Bus :i) It is bidinectional and group of wines which countries control signal from processor to perlipheral & vice-versa. ii) Control the access to and use the address line & data lines. iii) control signal like memory read, write & I/O read, write etc. Bus Stuvetone: -11 is of two types i) Single Bus Structure ii) Multi Bus Structure 1) Single Bus Structure: is it is a simplest way to increment functional unit at a 2) common bus is used to communicate between peripheral and processor 3) Single bus does not one transfer at a time so that only two units can actively used the bus at a given time. input memory processor pulput

Advantage:-1/11 is simples & low cost 2) Very flexible for attaching puipheral devices. Musbachs :i) Speed gets slow because devices connected to the Bus very widely in their speed of operation. is Ettikient transfer at a time so that only two units can actively used the Bus of given time , is Efficient transfer mechanism is needed to solve their problem iii) Common approach is to include bugger resistor with the durice to hold the information during transfer. ii) Mutti Bus Structore :-1) System that conteins multiple buses to achines more parallel that leads to betty performance but increase the cost 2) In multiBus structure each of which connects subset of module eq: In two Bus structure bus can be used to fetch instruction other can be used to fetch data to nequined for execution. linput Memory prioce ssor Output 1/0 Bus (Two Bus Structure)

(Small computer system interface): SCST i) Sess full form is "small computer system intergace" ii) Standard pournates panallel but interdace for connecting peripheral device to a PC. iii) It can connect maximum 16 percipherals devices. i) It follows dairy chai Method (preis wity wise) V) Hand shaking of signals done by sest bus between devices requirering nequesting from both side VI) SCSI is used to increase performance, deliver faster data transfer transmission. v) Provide expansion for device such as Hard drave, UD-ROM, deriver, scanners, DVD Drivers, and cD whitters, take driver viii) SCSI has a contucller in charge of transferring data between device and scsI bus. vx it is either embedded on the Mother board or a host adapter is inserted into an expansion slot on the mother board x > SCSI is widely used in workstation, server. \* Mainframes it is less commonly used in desk-top Per. PHOCESSON Moin Memory . System Bus Bridge PCI Bus (periphere) control additional SCSI inter con-Memory controller ethernet USB nicted interface controller 17 video keyboard Mouse Disk2 Disk 1 cd Rom doiley chain Method

\* Phallel Bus: In this bus data transfer parallely which in verses the speed of transferring data.

USB Contuoller:

→ 1287 peripheral devices we can add

→ Same as SCSI controller

→ Maximum speed 480mbps speed.

→ Without hub 5 meter can travel

→ without hub 5 meter can travel

→ app: Keyboard, printer, Scanner

→ we can add mobile / tablet also.

## PARALLEL PROCESSING

1 86

<u>Social Computing</u>: Traditionally, software has been written for serial computations

i) To be rown on a single computer having a single central processing unit (CPU).

ii) A problem is broken into a discueste parts that can be series of instructions iii) Instruction are executed one after another

iv) Only one instruction May execute at any moment in time

Parallel Computing:-Parallel computing is the simultaneously use of multiple computing resources to solve a computational problem

is To be run using multiple CPUs.

ii) A problem is broken into discreate parts that can be solved concurrently.

iii) Each pants is further broken down a series of instructions iv) Instruction from each part execute simultaneously on different. (Pus

\* The real would is parallel: The real would is parallel: i) Complex, in the related events happen simultaneously E.g - galaxies, planetory movement, functioning of the brain wheather, traffic

ii) Parallel computing is better suited for Modeling, simultaneously these process. Need of parallel computing:i) Save time & money: Money nerources working together. will reduce the time and cut potential costs. Loop Lwel :iteration i) At this level consecutive loop interaction are the candidates for porallel executions is However, data dependencies between subsquent iterations May rest parallel execution of instruction at loop level. There is a lot of scope for parallel execution at loop lurch iii) Ex: In the following loop in C language for (i=0; i<=n; i++) A(i) = B(i) + c(i)iv) Each of the instruction A(i)=B(i) + (i) can be executed by different processing elements there are at least of processing elment. V) yowever, the instruction in the loop for (J=0, JK=n, J++) A(J) = A(J-1) + B(J)vi) cannot be executed in porrallel as a y is data dependent on A (J-1). This years that before exploiting the loop level parallelism the data dependencies must be checked.

Von Neumann Architecture: i) Non-Neumann puoposed his computer artitecture design in 1945 which was later known as Von-Neumann outitecture. ii) It consisted of a control unit, Anthmetic, and logical unit (ALU), resistors, Memory units & input /output units. The combination of ALU & control unit is called central processing unit or processing element (PE) iii) Von-Neumann autitecture is based on stoned - program computer concept, where instruction dates & program dates are stoned in the some Memory. This desing is still week in Most computer produced today. iv) A von-Neumann bessed computur: Memory 1) User a single processor conhol 2) Uses one memory for both instruction ALU unit ad & data 3) Executed priogramms following the fetch-decode executes yele input output V) compiled of your main components. The la bar (1) 1) Memory in in the 2) Control unit 3) Anthmetic logic unit statte set 4) Input/ Output (1), 小田村本 vi} Read/Write. (RAM) is used to toth program & instruction & data 1) Program instruction our coded date which tell the computer to do something. a) 1) at is simply information to be used by the program vii) control unit fetches instruction/data from memory, decode the instruction and they sequentially co-ordinates operations to accomplish the program task.

ii) When the stage s, is neady to transmit it sends a neady signal - Lo stage Siti. After Sit, He cieves the inconting data, it return acknowledgement signal (Ack) to SI. in) This pipeline are useful in designing communication channel for message parsing yulticomputer iv) This pipeline your have a variable throughput mater because different amount of delay may be experienced in different sterges different amount of stages. Synchuonous pipeline Model: i) In synchronous pipeline, clocked catches are used to interface between stages. Input L output TITATI SI TITATI sz mil man SK - + ----- tm -> d K-\*Si = Stage \* L= lateh ii) The pipeline consist of cascade of proceeding stage \* T = cluck period \* The receiment (Si). The pipeline stages are combinational circuits \* Stage delay performing arithmetic & logic operation over the \* q= latch dels date stream flowing through the pipe iii) The stages are separated by high speed interface latcher (L) The latches are just fast resistor for holding the intermediate result between the stages. iv) Upon arival of clock pulse latches transfer data to next stage withe utilization pattorn successive stages in this pipeline is specified by reservan table.

Multiprocessore There are your than one processor present in the system which can execute yoke than one processor at the same time CRU3 CPUN [CPU1] CPU21 Memory There are 2 types of Multipreocension: 1) Symmetric multiplus cessore is Asymmetric multiprocessory. Symmetric Multiphocesson: One operating system control all CPU. Each UPU has equal rights. All the CPU are in peut to peut relationship. Asymmetric Multiprocessor There is a marty predeers that gives instruction to all the other processor . It contains master-solve relationship. Advantages: i) Maximum throughput ii) Mone reliable system. iii) fast processing iv) Elficiency improved V) More econonic system. flynn's classification : It is based on the multiplicity of instruction stream & data stream in a computer system.

There are foun catagories that is: DSISD (Single instruction stream single data stream) ii) SIMD ( single instruction streeping rultiple data streeping) iii) MISD [ Multiple Instruction struam single data stream) i) MIMD (Multiple Instruction stream Multiple data stream) 1) I Flynns classification based on number of instruction & date ») Based on the notion of stream of information two types of information flow into a processor: instruction & dates 3) Instruction stream is defined as the sequence of instruction executed by processing unit. 4) Pata stream, is defined as the sequence of data including inputs, partial or temporary necesits, called by the instruction i) Single Instruction Single Data Stream (SISD). is a uni-processor yachine which is capable of executing a single instruction, operating on a single date stream. ii) conventional signal processore Von-Neumann computer are classified as SISD system. (i) It is serial (non-parallel) computer. iv) instruction are executed sequentially but may be overlapped in their execution stages (pipelining). Most SISD Uni-processing system are pipelined. v) Ex - most pi's, single CPU workstation, minicomputer etc. Instruction Struamico (15)0 15 Oprocenting dates control Main Unit unit

ii) Single Instruction Stream Multiple Data Stream (SIMD): 1) An SIMD systery is capable of executing the same instruction on all the CPUs but operating on different data at Stream. a) SIMD computer has single control unit which issue one instruction at a time but it has multiple All's or proceering units to cavery out on multiple data sets. 3) & - Annay phocesson and vector pipelines Anney processor = MPP, ILLIAC - IV Vector pipelines - 13M 9000, very x - Map, YMP/ C90. DUIK data stream MM, 11.14 DU2 K data stream 2 MM2 w SN data stream DUn MMn Instruction stream iii) Multiple Instruction Stream Single Data Stream (MISD): 1) In MISD Multiple instruction operate on single date stream. 2) the MISD computing system is capable of executing different instruction on different processing unit (PU) but all of them operating on the same data set. all. 3) MISD model are practically not useful in most of the applica? 4) Ex - Systolic ourays.

ISI YCU, 150 DU, PUZ 152 ISZY CU2 MM2 MM 2 lsn in Cun DUn Ъ2 i) Multiple Instruction Structure Mulliple Deute Stucam (MIMD): 1) MIMD system is capable of executing multiple instruction on multiple data set. 2) MIMD system are parallel computer or processing several program. 3) Ex - super computer, networked parallel computer, (BM 370, Cray -2 1 and would shart a will Might lsi 151 (DSI) CUI > Du MM,  $\left[ \begin{array}{c} D \\ \upsilon_2 \end{array} \right] \xleftarrow{D \\ s_2} \xrightarrow{D \\ s_2} \xrightarrow{S_2} \xrightarrow{S_2}$ 152 152 CU2 MM2 1 ISN fcum) lsn [Dun] t MMIN

| Important Motes:                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Difference between cisc and<br>Cisc                                                                                                                                                                                                                                                                                                                       | RISC. Il ma l'and annagering à<br>l'anna il annagering à la ca<br>RISC. RISC.                                                                                         |

| Stands fou Complex Instruction<br>Set computer.                                                                                                                                                                                                                                                                                                           | Stand for Reduced Instruction ut<br>Computer                                                                                                                          |

| A large number of instructions<br>are present in the ortitecture<br>Variable-length encoding of the<br>instructions.<br>Ex-1A32 instruction size can<br>renge from 1 to 15 bytes                                                                                                                                                                          | Neury few instituctions are<br>present.<br>Fixed-length encodings of the<br>instituctions are used<br>Ex - 1A32, generally all instruction<br>one encoded as 4 bytes. |

| CISC supports annay                                                                                                                                                                                                                                                                                                                                       | RISC doest not support an array.                                                                                                                                      |

| Aruthmetic and logical operations<br>can be applied to both memory<br>and recgistor operands.                                                                                                                                                                                                                                                             | Ailthmetic and logical operations<br>only uses neglister operands.                                                                                                    |

| Ged condition codes are used<br>The stack is being used for<br>procedure arguments and return<br>addresses.                                                                                                                                                                                                                                               | No condition codes are used.<br>Registers are being used for<br>procedure arguments & return<br>address.                                                              |

| Detine:                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                       |

| Clock Cycle: It is simply a "cycle" on it is a single electronic<br>pulse of CPU. During each cycle, a CPU can perform basic<br>operation such as fetching, an instruction, accessing dates memory,<br>or writting dote.<br>Hit Rate: The chief reas unement of cache which is the percentage<br>of all accesses that are satisfied by the data in cache. |                                                                                                                                                                       |

| also known as "hit matio".                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                       |

Subhoutine: A set of instructions that are used supeatedly in a program can be registered to as submoutine only one copy of this instruction is stored in the memory. When a submoutine is required it can be called many times during the execution of a particular priogram. A call subsecutine instruction calls the submoutine

Macro: It is used to make a sequence of computing instructions available to the programmer as a single program statement, making the programming task less tedious and less event - prone

en and the terms of the second s